PCB设计中的高速模拟布局技术

关键的外卖

为最佳模拟信号性能设置PCB。

模拟布局的PCB位置和路由技术。

CAD工具,可以帮助您的PCB设计工作。

来自所有这些来源的模拟输入必须转换为数字输入

最重要的是,大批员工从传统的办公室转向在家办公,这表明我们在多大程度上真正生活在数字时代。从共享在线文件到视频会议,远程工作人员正在尽可能多地利用他们所掌握的计算机和网络。然而,仅仅因为我们都是数字时代的一部分,并不意味着我们生活在一个数字世界。

我们的世界充满了必须被模拟电子设备探测和捕捉的景象和声音。这些模拟信号必须转换成数字格式,由计算机和其他数字设备进行处理,然后才能在不同的网络上以电子方式共享。转换这些格式的工作属于pcb中的混合信号电路,根据今天的电子要求,他们有相当多的工作要做。以下是一些高速模拟布局技术,可以帮助混合信号PCB设计成功完成其任务。

混合信号PCB设计

从我们的所见所闻到温度和运动,不同的电子设备捕捉到的感官事件的数量已经无法计算。这些动作或事件中的每一个都被捕捉为模拟信号,然后必须在计算机等数字系统中进行转换处理。这个转换的工作属于模拟-数字在这些系统的混合信号电路板中使用的转换器。

模拟信号将根据其源的大小而变化。例如,相机或麦克风检测到的光或声音的量将改变所捕获信号的振幅。然而,模拟电路的信号依赖于连续的电压或电流,并依赖于在传输和接收过程中的精确控制来正确解释。相比之下,数字信号只有两个值;时断时续。这种结构允许在传输方式上有更大的误差范围,使其设计比模拟电路更容易。

PCB设计人员必须行使适当的模拟分离以及布局时的数字电路,以防止这两种信号类型相互影响。我们将继续研究不同的方法。

模拟布局需要紧凑的组件位置

高速模拟布局技术的组件放置和跟踪路由

模拟电路和数字电路的最终成功很大程度上取决于PCB设计中的层堆叠配置的好坏。高速信号需要在相邻层上有一个参考平面作为信号返回路径,以最小化噪声并提高信号完整性。因此,在配置板层堆叠时,需要考虑到总体位置,以确保在适当的层上有足够的路由空间。设计师可以依靠高速模拟布局技术来实现这一点,比如根据功能和电路块将组件分组在一起,创建一个平面图,作为实际组件布局的模板。这个平面图需要将数字电路和模拟电路彼此隔离功能分区,而组间的互连安排为最直接的路由。

随着平面图的完成,设计师可以直接进入组件的放置。请记住,目标是使路由尽可能简短和直接,因此各部分必须在其位置上进行相应的配置。下面是一些高速模拟电路布局技术和布局提醒,在使用模拟电路时要记住:

- 放置部件之间最直接的路由。

- 不要将部件放置在将被迫通过模拟电路路由数字信号的地方,反之亦然。

- 保持组件位置尽可能紧凑,以减少模拟迹线的长度。

- 记住要按说明书摆放零件为可制造性而设计(DFM)标准,由您的组装商推荐。

- 让噪音较大的部件,如adc,远离电路板的边缘,位于更中央的位置。

放置组件,然后路由是许多PCB设计人员使用的工作流程;然而,在模拟布局中同时放置和路由有时是有帮助的。不管怎样,这里有一些模拟跟踪路由的建议:

- 保持跟踪路由尽可能简短和直接。这种路由应该已经通过您所做的紧密组件放置来促进,并将有助于减少阻抗不匹配和信号反射的机会。

- 在模拟电路布线时使用较宽的走线宽度。

- 尽可能将模拟迹线限制在一个单板层。过孔可以产生电感,你在有过孔的层之间的过渡越少越好。

- 请勿将模拟线路穿过数字电路区域,或将数字线路穿过模拟区域。

- 尽可能将模拟和数字路由限制在它们的电路区域内。这将进一步减少混合信号串扰的机会。

模拟信号和数字信号路由的最后一条规则是,永远不要让迹线穿过参考平面的阻塞区域。由于信号返回路径差,通过参考平面上这些区域的路由会产生噪声。

在相邻层上通过此区域路由跟踪可能导致信号返回路径阻塞

模拟布局的电力输送网络建议

设计中的模拟和数字组件都需要清洁的电源,但高速pcb的PDN经常受到许多问题的困扰,例如瞬态振铃。这通常是通过在设计中包括大量的去耦电容器,并通过在堆叠中相邻放置接地层和电压层来提供高平面间电容来解决的。同样,如何配置板层堆叠对混合信号设计的成功至关重要。

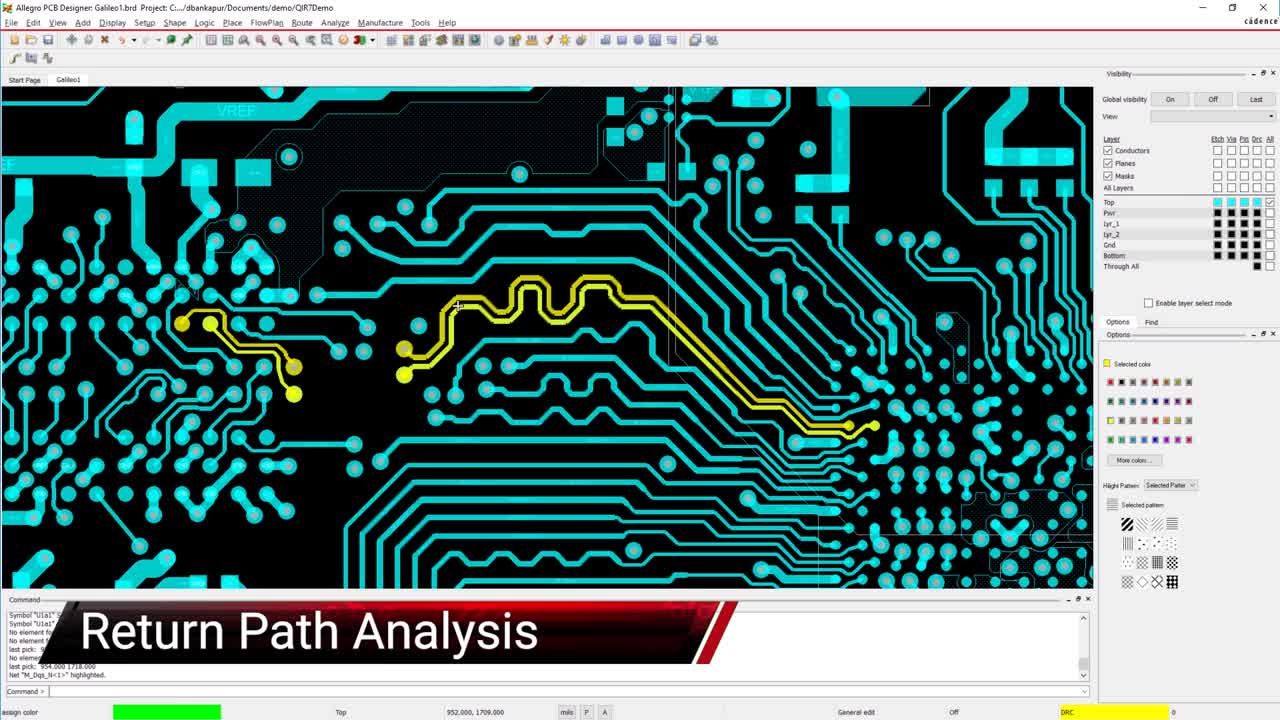

如何在你的设计中布局地平面对电路板的操作也是至关重要的。正如我们前面提到的,信号不应该在地平面被破坏的区域之间路由。无论是平面上的缝隙还是密集的过孔区域,如上图所示,地平面的破坏可能会阻塞信号的清晰返回路径,迫使它在返回源的路上徘徊。在设计中,这种漂移是产生EMI和降低信号完整性的主要原因之一。为了避免这些问题,请确保信号在接口上有清晰的返回路径参考面为了最好的董事会表现。设计工具,如Cadence的Allegro PCB Editor,具有帮助设计信号返回路径的高级功能,如本文顶部的视频所示。

对电路板上的信号返回路径造成很大问题的障碍之一是分裂的地平面。如果您的设计包含一个分割平面,请不要使分割与跟踪路由交叉。信号的返回路径将被完全切断,造成更严重的信号完整性问题。然而,更好的方案是根本不分割地平面。尽管许多人认为地面分割可以更好地隔离电路的模拟和数字区域,但它也会产生比预期更多的问题。我们已经提到了清晰信号返回路径的问题,如果使用底盘接地,也有可能在部分之间引入共模电流。相反,如果有一个完整的地平面,并且电路的模拟和数字区域分别放置和布线,那么对于那些必须在部分之间传播的少数信号,您将有明确的返回路径。消除地平面分割可以解决许多EMI问题,并为您提供更清晰的设计,因为模拟和数字信号将自然地在其轨迹周围形成紧密的返回路径。

显然,这样的设计需要在PCB布局过程中管理许多细节。使用先进的设计系统可以为设计师提供更高层次的帮助。

Cadence Allegro的约束管理器用于设置路由和通过设计规则

如何使用PCB CAD工具

将组件紧密地放置在精确的空间宽度上,并为模拟电路布线不同的迹线宽度和空间,需要详细的数据库管理。你会想要确保完全设置和使用您的CAD系统设计规则来控制这些约束。在上图中,您可以看到一个在Allegro中使用Constraint Management系统的示例,以及如何为组件间隙、轨迹宽度和单个元素或组件和网络的类别输入不同的值。

Cadence还可以帮助设计人员使用各种各样的电路仿真和设计分析工具。在Allegro中,您还可以查看和检查完整系统设计中的其他电路板或机械对象的3D PCB设计。有了这样的工具,设计师可以处理更复杂的设计,更快地完成它们,错误更少。

要了解更多关于成功的数字和模拟设计如何依赖于高速模拟布局技术以及设计良好的PDN,请参阅我们的电子书关于这个话题。

如果您想了解更多Cadence如何为您提供解决方案,和我们的专家团队谈谈吧.