设置PCB组件放置公差

关键的外卖

PCB组件放置公差从构建正确的占地开始。

电气放置公差对于电路板在其峰值性能下运行是必不可少的。

高产量PCB制造取决于PCB组件放置公差的遵守情况。

PCB组件放置公差对于电路板的最佳性能至关重要

“容忍”这个词可以有很多不同的含义,这取决于它在不同的语境中使用。作为父母,我的忍耐力通常是我的孩子们试图达到的极限。类似地,在电子设计中,公差通常也被尽可能地推到不损坏的程度。当然,问题是当超出公差时,设计会发生什么。

当放置组件在印刷电路板上,必须保持特定的间隙公差。这些公差包括CAD系统中组件占地面积的规格,组件如何定位以获得最佳电气性能,以及如何放置部件以实现电路板的可制造性。让我们仔细看看这些PCB组件放置公差,以及如何设置您的设计工具来适应它们。

PCB组件公差

在我们查看元件如何放置在电路板上的不同公差之前,我们需要首先从零件的公差开始。

CAD系统中的每个组件必须根据其制造商的规格来构建。如果CAD足迹构建不正确,实际的物理部分可能不适合电路板的金属地面图案。诸如此类的问题会导致电路板无法制造。

在PCB设计系统中构建组件足迹包括两个步骤:

- 创造金属土地的模式这个零件的引线会焊在上面。土地格局尺寸有时可以在制造商的数据表中找到,或者它们可能已经作为行业标准的土地格局存在,例如SOIC-14。

- 根据制造商数据表中的规格构建组件的物理形状或轮廓。

构建PCB CAD足迹是PCB布局中比大多数人意识到的更重要的部分,理解其中的原因非常重要。以0603封装中的标准旁路电容器为例。根据其密度的不同,您的设计可能需要数百个不同的旁路电容器,它们位于同一个0603封装中。在设计中只需要一个0603占地面积,CAD系统将为整个电路板的每个电容器实例复制它。但是,如果构建不正确,那么所有这些部分都将是错误的。如果占地面积建得太小,实际的部件可能甚至不适合电路板,而更大的占地面积可能会影响电容器在制造过程中的焊接方式。

为了避免PCB组件放置公差问题,在处理布局的PCB占地面积时,请记住以下指导原则:

- 面山(SMT)地面模式需要足够大,以在PCB组装期间促进良好的焊锡角。虽然这些土地模式通常在行业标准中规定,但有时您必须为特殊需求的部件创建自己的土地模式。在这种情况下,确保建立土地格局,以占用最小和最大销尺寸的部分。

- 通孔焊盘应该有一个足够大的钻孔,用于组件插入,但又足够小,以防止焊料从孔中吸起。

- 组件轮廓应构造到制造商数据表中规定的最大材料宽度。

- 此外,请记住,许多土地模式将不得不用于不同制造商的同一部分。在这种情况下,您将需要使用多个数据表,以确保您允许所有部件的最大材料宽度。

在这一点上,您的设计应该有良好的PCB占地面积,所以让我们看看部件之间的放置公差,以获得最佳的电路板电气性能。

CAD足迹需要建立精确的规格,以确保其适合性和可制造性

电气设计性能的放置公差

当在PCB布局中放置组件时,要记住的一个考虑因素是组件在其他部分的功能。例如,电源组件有严格的放置要求,以确保产生尽可能少的噪音和电磁干扰。这些部分一定要坚持好可制造性设计(DFM)要求在他们的位置,但他们也必须安排他们的最佳功能。以下是一些一般的放置规则,以确保电路的最大性能:

- 电源组件应尽可能紧密地保持在一起,以减少其迹线长度。电源中较短和较宽的走线降低了电感和减少电磁干扰(EMI)。

- 大引脚高速器件的旁路电容器需要尽可能靠近器件的电源引脚。这种接近将有助于减少电流峰值和由此产生的地面反弹信号完整性问题。

- 通过信号通路连接的高速器件必须紧密放置,以防止信号通路在单板上徘徊。一个紧密放置的信号路径将有助于确保低阻抗在高速传输线。

- 保持功能分区的组件在一起,除非信号在功能区域之间交叉。这将防止模拟噪声污染数字电路,反之亦然。

- 为热管理在美国,处理器和存储芯片等热运行的部件要靠近电路板的中心,并将电源电路分开。

这些PCB组件放置公差建议旨在帮助您的电路板发挥最佳性能。然而,电路板仍然需要可制造,需要一套完全不同的放置公差。

可制造性的PCB组件放置公差

即使你的电路板有最好的PCB占地面积和精确的放置和路由组件的性能,如果电路板最终不能被制造出来,这都是徒劳的。为了确保电路板的可制造性,必须遵守元件放置公差的四个关键原因。

组件与组件间距

部件之间放置太近可能会给以下制造过程带来潜在的问题:

- 自动化装配:用于在电路板上安装组件的挑选和放置机器将很难安装靠得太近的部件,需要手动安装这些部件。

- 波峰焊接:小的离散部件需要小心地放置在板通过波的方向上。两个引脚部分应放置,使两个引脚同时进入波。较大的部件不应在较小部件之前进入波,以防止阴影,导致焊点不良。

- 调试和返工:较小的组件不应该放在较大的组件下面,以帮助组装技术人员在电路板上调试和返工。

组件到板边缘间隙

由于以下原因,在靠近电路板边缘放置组件时也必须小心:

测试:靠近板边缘的部件可能会干扰测试夹具的真空下降。

板:过于接近电路板边缘的组件将需要一个断开标签,而不是v型槽来解除镶板。对于带连接器的板,这是预期的。否则,v型槽是一种更经济的方法,从面板分离板。电路板边缘也需要保持足够的间隙,以防止器件或金属电路在拆板过程中开裂。

热:靠近板边缘的部件可能会干扰所需的预期气流冷却单板.

测试点清理

虽然不是物理组件,但测试点需要放置在与它们接触的测试夹具探针不会与电路板上的部件碰撞的地方。测试点之间还需要有足够的间距,以便测试夹具探头。

人类访问

大多数电路板都有接口部件,这些部件必须由人手来操作。交换机必须设置,连接器将插入和拔出,某些网络将需要用手动测试设备探测。这些部件不仅需要放置在用户可以访问它们的地方,而且还需要与其他部件保持足够的距离,以使用户不会在此过程中对其他部件造成附带损害。

这些DFM问题通常可以在原型板上解决,在原型板上,快速转向对推出新产品至关重要。但当电路板进入正常生产时,需要纠正这些问题,以帮助降低制造时间和成本。值得庆幸的是,PCB CAD系统中有一些功能和实用程序可以提供帮助。

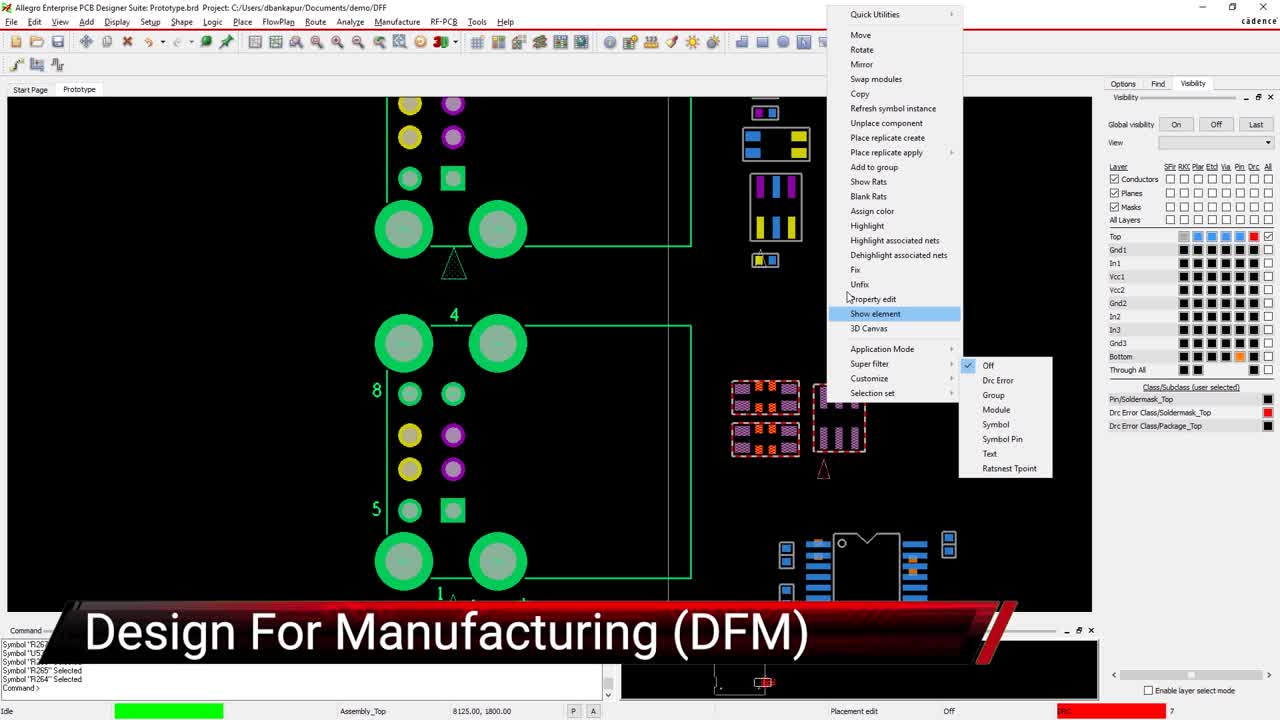

使用CAD系统的DRC功能可以为您省去很多麻烦,如Cadence Allegro所示

使用PCB设计工具管理组件放置公差

统一搜索实用程序,在Cadence Allegro设计工具中可用

正如我们所看到的,使用准确的PCB占地面积对于保持正确的组件放置公差至关重要。有一些辅助工具可以帮助实现这一点,包括行业标准和足迹创建向导,但最好的方法之一是使用外部库服务。高级PCB设计系统通常有一个实用程序,允许设计人员直接连接到外部库服务,以搜索和下载CAD模型。在上图中,您可以看到在Cadence设计工具套件中找到的统一搜索实用程序的图片。使用统一搜索工具,设计人员可以找到他们正在寻找的零件,并下载制造商的原理图符号、SPICE模型、数据表、零件信息、图像和PCB足迹。此实用程序将有助于确保布局获得正确的占地面积,以匹配原理图中使用的组件。

在这些设计工具中还有其他有用的功能也可以提供帮助。其中之一是约束管理系统,可设置为不同的组件间隙。您不仅可以设置组件到组件的清理,还可以设置组、区域甚至特定部件的清理。像这样的约束系统将允许您的设计规则检查(DRCs)提醒您组件放置间隙不在公差范围内,并帮助您设计更好的电路板。

要了解更多关于PCB布局和可制造性设计的信息,请看看这个电子书.

如果您想了解更多Cadence如何为您提供解决方案,跟我们和我们的专家团队谈谈吧.