PCB布局的一些关键设计规则

关键的外卖

PCB设计中的设计规则和在线检查。

为组件放置和跟踪路由设置规则和约束。

利用设计规则进行三维校核。

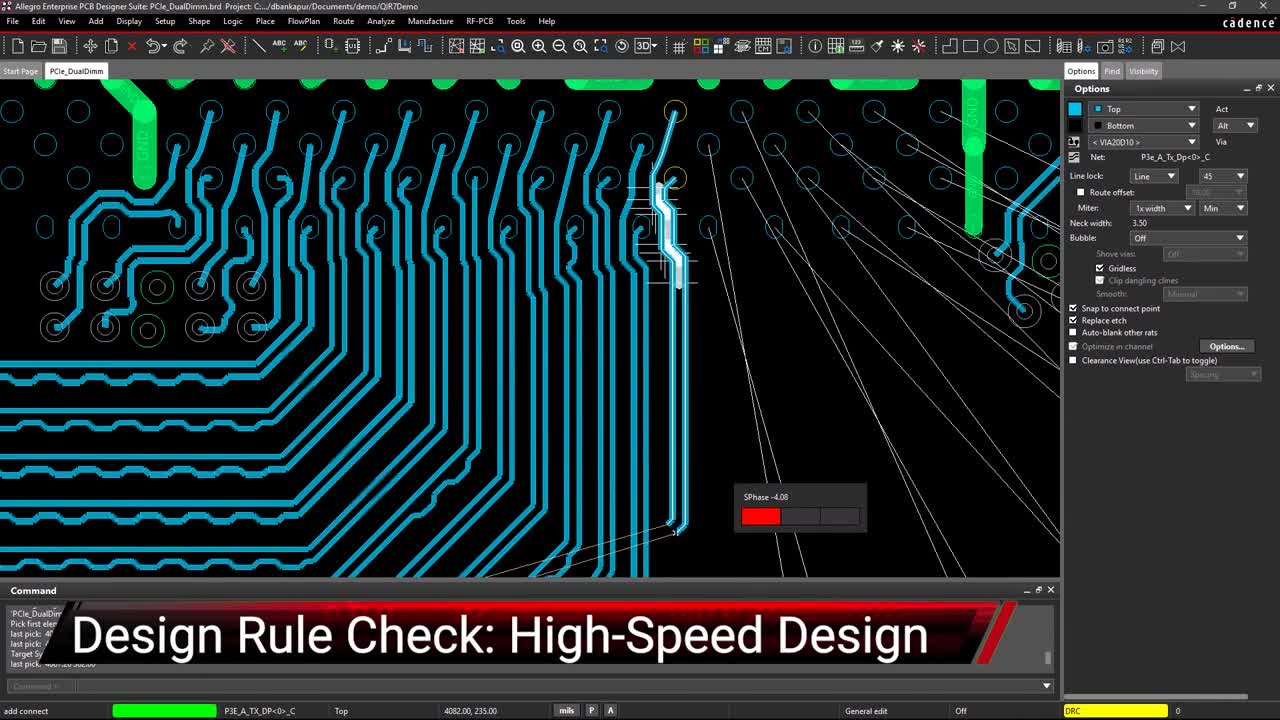

像这样密集的PCB路由需要一整套设计规则和约束来保持它的组织

对于孩子来说,最难学到的人生教训似乎是“规则不是为了剥夺你的乐趣,而是为了防止你受到伤害。”而且,即使孩子们说他们理解了这一课,下次他们因为你在街上玩耍而对他们大喊大叫而翻白眼时,他们就会证明他们真的没有理解。然而,这个建议不只是给孩子们的——它对电路板布局设计师也有非常现实的应用。

PCB设计CAD工具有内置的设计规则和约束管理系统,正如我们告诉孩子们的那样,这些规则是为了防止我们受到伤害。电路板在制造过程中出现故障,因为组件距离太近到板的边缘或因为太吵而导致适当的痕迹间隙不被使用是极其令人沮丧的。设计规则到位,以确保我们布局的电路板将避免这些问题和功能预期。在本文中,我们将看看PCB布局的一些关键设计规则,这些规则将帮助您避免这些潜在的问题。

PCB设计中设计规则和在线检查的重要性

设计和制造一个功能良好的印刷电路板有许多不同的难题。这些包括如何将零件放置在电路板上,如何在零件之间布线,以及如何通过电气方式一起工作以使电路板工作。设计规则的存在是为了确保所有这些部分正确地组合在一起以完成谜题。通过运行规则检查命令,可以在设计的任何部分检查设计规则,该命令将向设计人员报告发现的任何问题。这些规则也被自动在线检查系统使用,它会立即通知设计师,他们试图移动或编辑的内容是不允许的规则。

以保证板能由PCB制造商对于装配者来说,可以建立的规则的一部分是可制造性设计,或DFM规则。这些规则包括PCB制造、组装和测试(DFF、DFA和DFT)的独特设计规则。它们包括组件之间的距离,测试点可以放置在哪里,以及其他特定于制造的规则。这些设计规则还允许布局团队设置标准或默认,跟踪路由宽度,和空格值。这些规则可能看起来非常基础,但它们对于成功地布置棋盘是绝对必要的。在线检查系统在电路板路由时使用这些值,以防止设计人员意外地将不属于一起的迹线连接在一起,如下图所示。

设计规则系统的另一部分是电气约束,可以作为规则添加到设计中。它们控制跟踪路由的物理属性,以确保电信号在正确的时间到达目的地,并且不会受到串扰或其他信号完整性问题的污染。以下是一些可以设置的约束条件:

测量的迹长

匹配迹线长度

跟踪路由拓扑

差动对跟踪路由

层规则,唯一的间距和特定的宽度可控阻抗路由

电网规则更宽的宽度和间隙

高速信号路径

跟踪计时或调优

接下来,让我们来看看PCB布局的一些关键设计规则,从原理图中的规则应该如何开始。

在线drc可以防止PCB布局团队犯各种不同的路由错误

一套有组织的设计规则和约束从示意图开始

原理图应在每一张纸上捕获电路的逻辑设计流程。这不仅使PCB布局团队在电路板上布局电路时更容易遵循,而且它的组织也有助于创建原理图网络类和设计规则。大多数设计系统都为用户提供了从原理图中创建设计规则的方法,如果可以的话,您应该充分利用这一点。例如,网络,如存储总线或阻抗控制线,可以在网络类中组合在一起。虽然您可以将网络规则应用于单个网络,但将一组规则应用于整个组要容易得多。从那里,您可以为布局创建特定的跟踪宽度和间距规则,或者指定您希望遵循的某些跟踪属性,例如拓扑或长度。

还应确保所有这些信息都已准备好从布局示意图.这意味着检查是否所有部件都更新了,是否有适当的规则,并将原理图与PCB布局同步。这将有助于布局团队使用原理图进行交叉探测和网和引脚的选择。原理图还应包含关于特定规则和布局要求的注释和信息。有了这些数据,设计就可以由PCB布局团队添加剩余的物理规则和约束了。

使用设计规则和约束来管理组件占用之间的间距

充分利用CAD系统的PCB布局设计规则

每个PCB设计CAD系统都有自己的方法来建立设计规则和约束。出于我们的目的,我们将使用Cadence的Allegro PCB Editor中的约束管理器作为我们的例子。

约束管理器是一个电子表格风格的应用程序,可以在原理图编辑器和PCB编辑器中使用。在上面的图片中约束管理器用于设置PCB装配间隙。这些值将指示每个元件与电路板上其他元件或物体的距离。这对于组件放置至关重要,以确保您的最终板设计完全可制造。在图中,您还可以看到可以设置的附加组装约束以及用于设置PCB制造和测试的设计规则的菜单选择。在这里,您将能够为焊接掩模织带、锡膏覆盖范围、丝印覆盖范围和测试点间距。

在下面的图片中,您可以看到相同的Constraint Manager被用于为跟踪路由设置设计规则。在这种情况下,过孔被分配给各个网络,通过展开菜单,您将能够看到更多的设置,如迹宽和间距。这些相同的设置也可用于网络类、层或区域。还可以添加更多的约束,例如轨迹缩颈宽度、相同的净间距和差分对间距。此外,约束管理器可用于设置电气约束,包括以下内容:

信号完整性规则

时间限制

阻抗

传播延迟

返回路径

如您所见,在设计规则中可以设置大量的数据,以帮助确保您的电路板将被正确设计,并且可以毫无问题地制造。然而,除了所有这些,还有更多的PCB布局的关键设计规则,你可以使用,我们接下来将看看这些。

在Allegro约束管理器中通过分配显示不同的物理网络约束

将设计规则和约束提升到下一个层次

随着3D步骤模型的使用,布局团队现在有了PCB设计的视角,这在过去只可能与机械设计系统。借助CAD工具的3D功能,PCB设计人员可以更全面地了解他们的工作,从而具有发现意外组件冲突和碰撞的独特能力。这些工具还使PCB设计人员能够导入机械设计文件,以检查他们的电路板与整个系统设计的其他元素,包括其他PCB,电缆和系统插框。这些系统还能够通过对3D模型运行设计规则检查来搜索碰撞,如下图所示。

在Cadence的Allegro PCB编辑器的3D画布中的对象碰撞报告

PCB布局的设计规则可以打开一个全新的世界,允许你挑战技术的极限,但不能超越它。这使您可以自由地考虑设计中所有可能的场景,而不必担心您的努力是否违反了设计规则。要了解电路板设计现在如何与机械设计融合的更多信息,请查看这个电子书从节奏。

如果您想了解更多Cadence如何为您提供解决方案,跟我们和我们的专家团队谈谈吧.