探讨PCB焊锡掩模与粘贴掩模的区别

关键的外卖

PCB掩焊的基础知识。

了解锡膏在PCB上的作用。

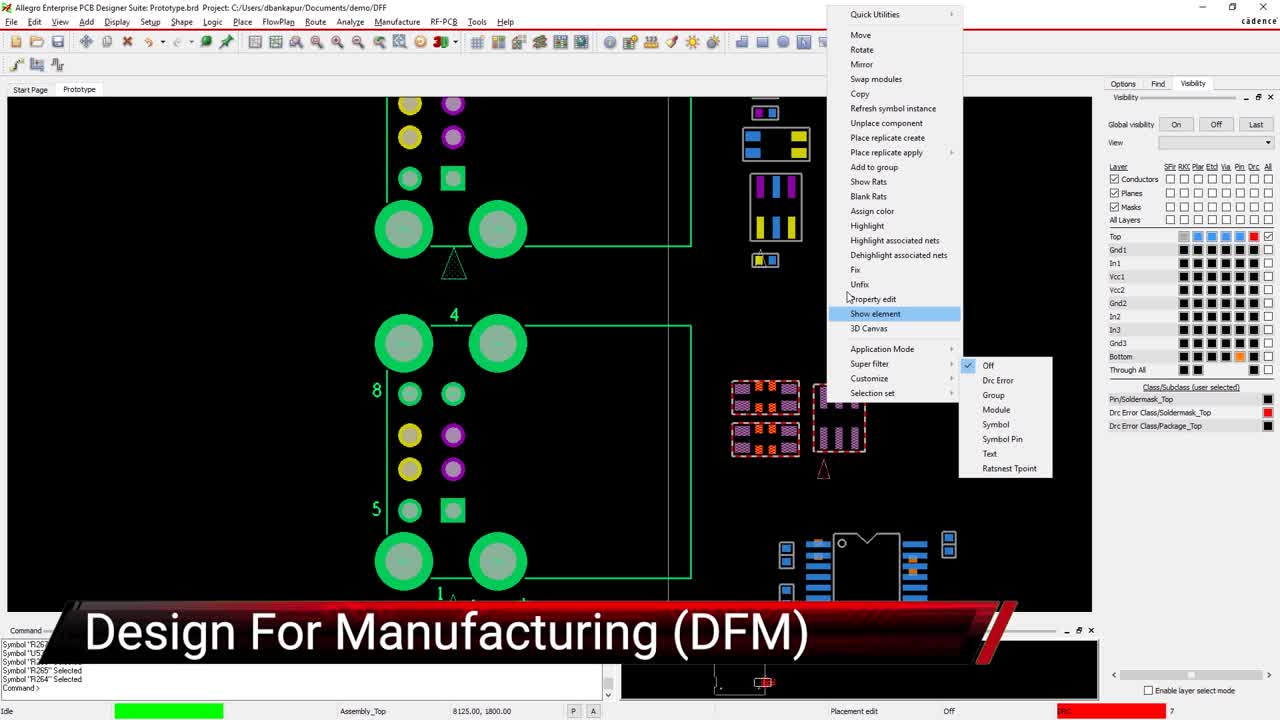

为焊锡掩膜和粘贴掩膜层设置PCB CAD系统。

激光切割不锈钢锡膏钢网

一个标准的印刷电路板通常需要两种不同类型的层,称为“掩模”。尽管它们都被称为掩模层,但焊接掩模层和粘贴掩模层是PCB制造过程中两个完全不同的部分所需要的。本文将讨论焊接掩膜与粘贴掩膜之间的区别,并详细说明PCB设计人员在使用这些层时需要知道什么电路板布局.

焊锡掩模和线路板制造

为了制造双面线路板,电介质芯材料被夹在两层铜连接之间,铜连接由组件焊锡垫、区域填充和连接痕迹组成。这种相同的基本结构用于多层线路板的层对,除了铜和介电材料更薄,不包括内层的焊盘。最终,所有这些层对组合在一起成为一个多层电路板孔钻,完成的电路板就准备好供组装工人安装电子元件。然而,在板被送到组装工之前,必须完成另一个步骤来帮助保护板:应用焊锡掩模。

焊锡掩膜,或一些制造商所称的抗焊锡,是一种应用于电路板外表面的保护材料。焊锡掩膜将覆盖电路板的整个表面,包括金属和介电材料,除了要焊接的焊垫和孔。这种覆盖物将保护电路板免受金属氧化,腐蚀,污垢,甚至人类接触的污染。两个金属裸露区域之间的焊料掩膜屏障也有助于防止焊料在开放区域之间架桥和在金属表面积累。

遮焊材料可以通过两个不同的过程应用到电路板上:

液体:使用丝网印刷工艺,可将掩焊材料直接涂在板上,它会变硬,使焊盘和钻孔暴露在外。

可感光的:可感光的焊锡掩膜材料既可以作为液体涂敷,也可以作为一层干膜涂敷。电路板暴露在紫外线下,除了那些焊片和孔。这种暴露使焊锡掩膜材料在整个板上变硬,而孔和焊盘上未暴露的材料则被洗掉。

树脂通常用于焊锡掩模材料,因为它们耐高温、湿度和焊锡。焊锡掩码通常为绿色,但对于那些希望使用不同颜色的电路板以识别不同生产步骤的原始设备制造商来说,也可以使用其他颜色。例如,原型电路板可能是红色的,而绿色表示常规生产单元。同样重要的是,掩焊材料应应用在正确的厚度,以确保均匀的应用和最佳的固化。接下来,我们将看看粘贴掩模,它在PCB组装中的作用,并看看它与焊接掩模的区别。

PCB CAD系统中遮焊层的图像

粘贴掩模和电路板组装

波峰焊接

有两种主要的方法将组件焊接到生产构建电路板上,第一种是波峰焊接。这个过程需要通孔部件插入他们的钻孔和表面贴装部件粘在他们的焊盘上的板。然后,电路板在传送带上运行,通过一台机器,该机器有一波熔化的焊料,电路板必须通过。这种波通过钻孔向上传导,焊接通孔部件,并在焊盘和表面安装部件的引线之间创建一个焊点。

回流焊

第二种工艺称为焊料回流,是使用膏体掩膜的地方。焊锡回流工艺从一层精心沉积在焊锡膏上的焊锡膏开始表面安装垫焊接。焊锡膏是一种由金属焊锡颗粒和具有腻子稠度的粘性助焊剂组成的材料。助焊剂不仅清洁电路板和要焊接的部件的焊接表面,而且它还充当粘合剂,将部件固定在适当的位置,直到焊接完成。当通过焊锡回流炉时,焊锡膏融化,然后形成一个坚实的焊点的部分,它一直以其粘性固定在原地。

在电路板上涂锡膏的方法主要有三种:

手动:对于PCB返工或有限的生产运行,如原型机,焊锡膏可以使用注射器手动涂抹。然而,这是一个非常劳动密集型和缓慢的过程,不实际的生产运行。

喷墨打印:利用PCB CAD系统的膏膜数据,喷墨打印机可用于在板上的每个表面安装垫上沉积锡膏。这是一个非常精确的操作,但不一定是最快的应用方法。

模板:对于大量生产电路板,制造商将使用来自PCB CAD系统的相同的粘贴掩模数据创建一个模板,就像用于喷射打印机一样。模板通常是用激光制作的,并经过不同材料的处理,以保证焊锡膏的应用精度和模板的长寿命。使用刮板,焊锡膏可以在不到一分钟的时间内应用到电路板上,是大批量生产最快的应用方法。

正如你所看到的,焊锡掩模和膏体掩模的主要区别在于,焊锡掩模是用于保护电路板的材料,而膏体掩模是用于应用焊锡膏的图案。接下来,我们将了解如何使用PCB CAD系统。

与上图相同的视图,只显示锡膏

PCB设计层:焊锡掩膜与粘贴掩膜

一个PCB CAD系统会使用不同的方法内部层用于表示顶部和底部焊接掩模以及顶部和底部粘贴掩模。CAD系统中的每一层都传递制造掩模、模板或用于在电路板上应用掩模和锡膏的图案所需的数据。

在上面的两张图片中,你可以看到PCB CAD焊接掩模层的绿色和粘贴掩模层的红色的例子。注意,焊锡掩膜图像比焊锡膏层包含更多的元素。这是因为您可以看到所有钻孔、通孔和将被焊接的表面安装垫,而粘贴掩模层只显示表面安装垫。焊点掩膜元件定义了不应用焊点掩膜的位置,而膏体掩膜元件定义了锡膏应用的位置。

在大多数情况下,PCB CAD系统中锡焊掩模和粘贴掩模层的创建都是自动化的。尽管PCB设计人员可以控制焊接掩模和粘贴掩模元件的大小和形状,但大多数人会选择使它们与PCB占地中的焊板或孔的大小相同。这就把改变这些元件尺寸和形状的责任放在了电路板制造和组装车间。然而,对于那些想要控制掩模元素的设计人员来说,这可以通过编辑PCB足迹或通过后处理例程运行数据来实现。现在,我们将看看如何在Cadence的Allegro PCB编辑器中创建焊接掩膜和粘贴掩膜层。

在Allegro PCB编辑器中的横截面编辑器显示膏体和焊锡掩模

与PCB CAD层工作

在Cadence的Allegro PCB编辑器中,用户可以完全控制其焊接掩码和粘贴掩码的形状和大小Padstack编辑器.这使设计人员能够添加、删除或编辑设计中使用的任何padstack元素。同时,可以在Constraint Manager中设置管理这些元素的规则。检查制造和装配规则将提醒设计人员注意可制造性问题,如在细间距焊盘之间没有足够的焊锡掩膜,以防止焊锡桥接。

配置设计与正确的焊掩膜和膏掩膜层是在横截面编辑器中完成的。在上图中,你可以看到编辑器中显示的设计的图层堆叠,包括不同的蒙版层。这些层可以配置宽度和材料信息,以帮助层堆叠计划的制造。

要了解更多关于层堆叠策略的信息,这将有助于您的电路板的可制造性规则(DFM)的设计,看看这个电子书从节奏。如果你想了解更多关于Cadence如何为你提供解决方案,和我们的专家团队谈谈.